SISD - Single Instruction Single Data

SIMD - Single Instruction Multiple Data

SIMD 는 하나의 명령어로 여러개의 데이터를 처리하는 것을 말한다

SISD는 하나의 명령어로 하나의 데이터 처리

예를 들어 c언어에서 두개의 변수를 더하는 명령어 + 는 두개의 변수를 더하는 즉 하나의 명령어로 두 변수를 더해 하나의 변수에 결과를 저장한다

만약 8개의 덧셈을 한다고 한다면 cpu 8 클럭이 지난 후에 8개의 덧셈 연산이 완료 되지만

SIMD 는 1 사이클에 8개의 변수와 상응하는 값을 덧셈연산 할 수 있다

PADDW 는 SIMD 에서 덧셈 연산을 말하며

MOVDQU XMM0, A 에서의 A 는 short 형 크기 8개가 나열된 배열이라고 보면 된다

이 경우 두개의 변수를 더하게 되면 한사이클로 위 그림처럼 8 개의 덧셈을 처리할 수 있다

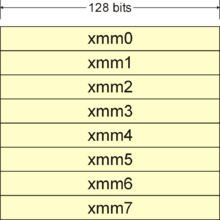

이런 연산이 가능한것은 SIMD 를 사용하게 되면 CPU 에서 사용하는 연산을 위해 사용되는 범용 레지스터외에 XMM 이라는

특수한 레지스터를 사용하기 때문에 이러한 처리속도의 이득을 얻을 수 있다

- SIMD 는 xmm0~xmm7 번의 레지스터를 사용하며 각 레지스터의 크기는 16byte 이다 (128 bit)

- 언어는 어셈블리로 SIMD 명령어를 사용하거나 C함수에서 Intrinsic 함수를 사용하거나 C++ 에서 Vector Class 를 사용한다

SIMD 는 Intel 과 AMD 에서 사용가능

스트리밍 SIMD 확장

스트리밍 SIMD 확장(Streaming SIMD Extensions, SSE)은 x86 아키텍처에 대한 SIMD(단일 명령 다중 데이터) 명령어 집합 확장이며, 인텔이 1999년에 펜티엄 III 시리즈 프로세서에 도입하였다. 이 기능은 1998년 등장한 AMD사의 3D나우! 기술에 대응한다. SSE는 70가지의 새로운 명령어와 추가적인 레지스터로 구성되며, 명령어의 대부분은 부동 소수점에 대한 연산이다.

SSE는 펜티엄 III가 코드명 Katmai로 알려져 있을 시기에는 KNI(Katmai New Instructions)로 불렸다. 이후 이 이름은 ISSE(Internet Streaming SIMD Extensions)로 정해졌었으며, 이후 SSE로 변경되었다. AMD는 애슬론 XP와 듀론 프로세서를 기점으로 SSE 명령 지원을 추가했다.

레지스터

SSE는 x86 아키텍처에서 XMM0~XMM7의 8개의 128비트 레지스터를 추가한다. 또한 x86-64에서는 XMM8~XMM15의 8개의 레지스터가 추가되었다(단, 이 레지스터는 64비트 모드에서만 사용가능하다). 추가적으로, 32비트 레지스터 MXCSR는 SSE 명령어의 상태 및 제어에 사용된다.

SSE는 XMM 레지스터의 자료구조로 4개의 32비트 단정도 부동 소수점을 사용했다. 즉, 하나의 레지스터에 4개의 값이 들어가는 형태였다. SSE에서는 정수 계산을 지원하지 않는다. 이것은 MMX 명령어를 사용하는 방식으로 극복이 가능했다. 또한, SSE2부터는 SSE를 확장하여 다음의 자료구조를 지원한다.

- 2개의 64비트 배정도 부동 소수점

- 2개의 64비트 정수

- 4개의 32비트 정수

- 8개의 16비트 정수

- 16개의 8비트 정수

SSE를 처음 지원한 펜티엄 III는 SSE와 FPU를 동시에 사용할 수 없도록 만들어졌다. 이러한 구조는 명령어 파이프라인 효율성을 떨어뜨렸다.

XMM 레지스터는 태스크 스위치 시에 값을 보존해야 하는 대상이기 때문에, 운영 체제가 이 레지스터를 사용하도록 명시적으로 활성화하기 전까지는 사용이 불가능하다. 다시 말하면, 운영 체제가 SSE 레지스터를 보존하는 명령어인 FXSAVE와 FXSTOR를 사용할 수 있어야 한다는 의미이다. 이러한 지원은 주요 IA-32 운영 체제에서 빠르게 추가되었다.

SSE 명령어

- 부동 소수점 명령어

- 메모리 대 레지스터 / 레지스터 대 메모리 / 레지스터 대 레지스터 데이터 이동

- Scalar – MOVSS

- Packed – MOVAPS, MOVUPS, MOVLPS, MOVHPS, MOVLHPS, MOVHLPS

- 산술

- Scalar – ADDSS, SUBSS, MULSS, DIVSS, RCPSS, SQRTSS, MAXSS, MINSS, RSQRTSS

- Packed – ADDPS, SUBPS, MULPS, DIVPS, RCPPS, SQRTPS, MAXPS, MINPS, RSQRTPS

- 비교

- Scalar – CMPSS, COMISS, UCOMISS

- Packed – CMPPS

- 데이터 셔플 / 언패킹

- Packed – SHUFPS, UNPCKHPS, UNPCKLPS

- 자료형 변환

- Scalar – CVTSI2SS, CVTSS2SI, CVTTSS2SI

- Packed – CVTPI2PS, CVTPS2PI, CVTTPS2PI

- 비트 논리 명령어

- Packed – ANDPS, ORPS, XORPS, ANDNPS

- 메모리 대 레지스터 / 레지스터 대 메모리 / 레지스터 대 레지스터 데이터 이동

- 정수 명령어

- 산술

- PMULHUW, PSADBW, PAVGB, PAVGW, PMAXUB, PMINUB, PMAXSW, PMINSW

- 데이터 이동

- PEXTRW, PINSRW

- 기타

- PMOVMSKB, PSHUFW

- 산술

- 다른 명령어

- MXCSR 관리

- LDMXCSR, STMXCSR

- 캐시 및 메모리 관리

- MOVNTQ, MOVNTPS, MASKMOVQ, PREFETCH0, PREFETCH1, PREFETCH2, PREFETCHNTA, SFENCE

- MXCSR 관리

예

다음 예는 SSE의 장점을 보여준다. 컴퓨터 그래픽등에서 아주 자주 사용하는 명령어인 벡터 더하기를 보자. 두개의 단밀도를 더하기 위해서는 x87를 사용하는 4개의 구성요소 벡터가 4개의 부동소수점 더하기 명령어가 필요하다.

vec_res.x = v1.x + v2.x;

vec_res.y = v1.y + v2.y;

vec_res.z = v1.z + v2.z;

vec_res.w = v1.w + v2.w;

이것은 오브젝트코드에서 4개의 x87 FADD명령어에 해당한다. 반면에 다음 수도 코드(pseudo-code)에서는 하나의 128비트 ‘packed-add’ 명령어가 4개의 스칼라 더하기 명령어를 대체한다.

movaps xmm0,address-of-v1 ;xmm0=v1.w | v1.z | v1.y | v1.x

addps xmm0,address-of-v2 ;xmm0=v1.w+v2.w | v1.z+v2.z | v1.y+v2.y | v1.x+v2.x

movaps address-of-vec_res,xmm0

뒤에 나온 버전

같이 보기

| [숨기기] 명령어 집합 확장 | |

|---|---|

| SIMD (RISC) | |

| SIMD (X86) | |

| 비트 조작 | |

| 코드 밀도 | |

| 보안 및 암호 | |

| 트랜잭셔널 메모리 | |

| 가상화 | |

https://ko.wikipedia.org/wiki/%EC%8A%A4%ED%8A%B8%EB%A6%AC%EB%B0%8D_SIMD_%ED%99%95%EC%9E%A5#SSE_%EB%AA%85%EB%A0%B9%EC%96%B4

'운영체제 & 병렬처리 > TBB & SIMD' 카테고리의 다른 글

| SIMD 연산구조와 성능 (0) | 2018.02.09 |

|---|---|

| Pack 과 Package (0) | 2018.02.09 |

| 왜 스레딩 빌딩 블록인가 (0) | 2012.11.02 |

| TBB 환경설정 threading building blocks (0) | 2012.11.02 |

| [TBB] 기본 알고리즘 (0) | 2012.11.02 |